# **DSP PRODUCTS DATABOOK**

DSP PROCESSORS MICROCODED SUPPORT COMPONENTS FLOATING - POINT COMPONENTS FIXED - POINT COMPONENTS

- DSP Processors 2

- Microcoded Support Components 3

- Floating-Point Components 4

- Fixed-Point Components

- **Package Information**

- Application Notes 7

- Appendix |

# 1989 DSP Products Databook

©Analog Devices, Inc., 1989 All Rights Reserved

5

6

### DSP PRODUCTS DATABOOK April 1989

### © Analog Devices, Inc., 1989 All Rights Reserved

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Products in this book may be covered by one or more of the following patents. Additional patents are pending.

RE29,619, RE29,992, RE30,586, RE31,850, DES. 233,909, 3,007,114, 3,278,736, 3,355,670, 3,441,913, 3,467,908, 3,500,218, 3,530,390, 3,533,002, 3,685,045, 3,729,660, 3,793,563, 3,803,590, 3,842,412, 3,868,583, 3,890,611, 3,906,486, 3,909,908, 3,932,863, 3,940,760, 3,942,173, 3,946,324, 3,950,603, 3,961,326, 3,978,473, 3,979,688, 4,016,559, 4,020,486, 4,029,974, 4,034,366, 4,054,829, 4,092,698, 4,123,698, 4,136,349, 4,141,004, 4,213,806, 4,250,445, 4,268,759, 4,270,118, 4,286,225, 4,309,693, 4,313,083, 4,323,795, 4,338,591, 4,349,811, 4,363,024, 4,374,314, 4,383,222, 4,395,647, 4,399,345, 4,400,689, 4,400,690, 4,427,973, 4,439,724, 4,460,891, 4,475,103, 4,475,169, 4,476,538, 4,481,708, 4,484,149, 4,485,372, 4,491,825, 4,511,413, 4,521,764, 4,543,560, 4,543,561, 4,547,766, 4,547,961, 4,556,870, 4,558,242, 4,562,400, 4,565,000, 4,586,019, 4,586,155, 4,590,456, 4,596,976, 4,601,760, 4,604,532, 4,608,541, 4,622,512, 4,626,769, 4,639,683, 4,644,253, 4,646,056, 4,646,238, 4,678,936, 4,684,922, 4,685,200, 4,694,276, 4,697,151, 4,703,283, 4,707,682, 4,709,167, 4,717,883, 4,722,910, 4,742,331, 4,751,455, 4,752,900, 4,761,636, 4,769,564, 4,771,011, 4,774,685, 4,791,551

France:

111.833, 70.10561, 75.27557, 76 08238, 77 20799, 78 10462, 79 24041, 80 00960, 80 11312, 81 02661, 81 14845, 82 09758, 83 03140

Japan:

1,092,928, 1,242,936, 1,242,965, 1,306,235, 1,337,318, 1,401,661, 1,412,991

West Germany:

2,014 034, 25 40 451.7, 26 11 858.1

U.K.:

1,310,591, 1,310,592, 1,537,542, 1,590,136, 1,590,137, 1,599,538, 2,008,876, 2,032,659, 2,040,087, 2,050,740, 2,054,992, 2,075,295, 2,081,040, 2,100,081, 2,103,884, 2,104,288, 2,107,951, 2,115,932, 2,118,386, 2,119,139, 2,119,547, 2,126,445, 2,126,814, 2,135,545, 2,137,787

Canada:

984,015, 1,006,236, 1,025,558, 1,035,464, 1,054,248, 1,141,034, 1,141,820, 1,142,445, 1,143,306, 1,150,414, 1,153,607, 1,157,571, 1,159,956, 1,177,127, 1,177,966, 1,184,662, 1,184,663, 1,191,715, 1,192,310, 1,192,311, 1,192,312, 1,203,628, 1,205,920, 1,212,730, 1,214,282, 1,219,679, 1,219,966, 1,223,086

Sweden: 7603320-8

# General Information Contents

Deer

1

|                      | Lage  |

|----------------------|-------|

| General Introduction | 1 – 2 |

| Table of Contents    | 1 – 3 |

- - --

# Introduction

### DSP AT ANALOG DEVICES

Analog Devices is the industry's leading supplier of high performance signal processing integrated circuits. As the leader, Analog Devices was quick to recognize the important opportunities made possible by the growth of digital signal processing. In 1983, the DSP Division introduced the industry's first CMOS fixed-point multipliers and multiplier-accumulators. These matched the speed of bipolar alternatives while cutting power requirements by a factor of twenty. This breakthrough shifted the focus of the industry from bipolar to CMOS for high speed VLSI circuits.

### **PRODUCT GROWTH & INNOVATION**

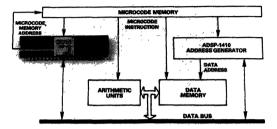

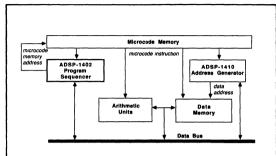

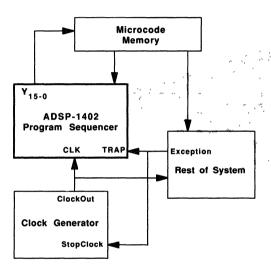

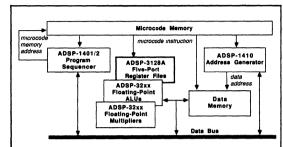

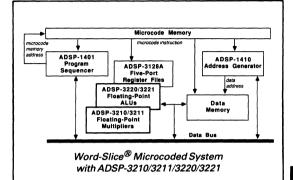

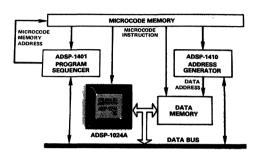

From a base in industry-standard components, we brought out a complete line of building block VLSI processors for high end DSP and numeric processing systems. These include several 64bit IEEE floating-point chipsets and a single-precision (32-bit) version of one of the same chipsets. Other products in the family are an address generator, two program sequencers and a register file.

In 1986 we introduced the first full off-chip Harvard architecture DSP microprocessor, the ADSP-2100, complemented by a superior set of interactive development tools.

### **TECHNOLOGY GROWTH**

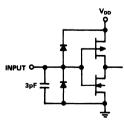

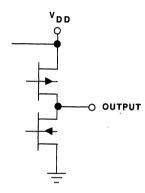

From our original CMOS wafer fabrication in 5 micron geometries we moved, in 1985, to 1.5 micron double-layer metal CMOS. We are currently in production with both the 1.5 micron and our newer 1.0 micron CMOS processes. Our 12.5MHz ADSP-2100A is the 1.0 micron version of our original 1.5 micron ADSP-2100, for example. Analog Devices continues to develop advanced processes such as specialized bipolar and gallium arsenide both internally and through our strategic investments.

Our manufacturing facilities include factories in Wilmington, Massachusetts and assembly in the Philippines. Our digital VLSI test capability is located in Norwood, Massachusetts, the Division's headquarters.

### **APPLICATIONS & SUPPORT GROWTH**

Analog Devices supports its products with a technically strong direct sales force and readily available applications assistance. Our Applications Engineering staff in Norwood, Massachusetts; Santa Ana, California; Tokyo, Japan; Newbury, UK and other locations worldwide understands the specialized requirements of designing and supporting DSP systems. Our quarterly DSP applications newsletter, *DSPatch*, brings you up-to-date applications and is available free by request.

### DSP PRODUCTS DATABOOK

This book provides complete technical data on DSP products from Analog Devices. Included are:

- Comprehensive Data Sheets on some 20 significant product families

- Selection Guides for rapid product finding

- DSP Application Notes

- List of available Technical Publications on real-world analog and digital signal processing

- Worldwide Service Directory

- Index.

Besides this Databook, the present series includes a Linear Products Databook and a Data Conversion Products Databook; like this book, the latest versions of both are available free upon request.

### **TECHNICAL SUPPORT**

Our extensive technical literature discusses the technology and applications of products for precision measurement and control. Besides tutorial material and comprehensive data sheets, including a large amount in our Databooks, we offer Application Notes, Application Guides, Technical Handbooks (at reasonable prices), and several serial publications; for example, Analog Productlog provides brief information on new products being introduced, and Analog Dialogue, our technical magazine, provides in-depth discussions of new developments in analog and digital circuit technology as applied to data acquisition, signal processing, control, and test. We maintain a mailing list of engineers, scientists, and technicians with a serious interest in our products. In addition to Databook catalogs, we also publish several short-form catalogs on specific product families. You will find typical publications described on pages 8-2 and 8-3 at the back of the book.

### SALES OFFICES

Backing up our design and manufacturing capabilities and our extensive array of publications is a network of sales offices and representatives throughout the United States and most of the world. They are staffed by experienced sales and applications engineers, and many of them maintain a local stock of Analog Devices products. Our Worldwide Service Directory, as of the publication date, appears on pages 8-6 and 8-7 at the back of the book.

### RELIABILITY

The manufacture of reliable products is a key objective at Analog Devices. We maintain facilities that have been qualified under such standards as MIL-M-38510 for ICs in the U.S. and Ireland and MIL-STD-1772 for hybrids. A growing number of our products have qualified for JAN part numbers; others are in the process. Most of our ICs are available in versions that comply with MIL-STD-883C Class B.

We publish a *Military Products Databook* for designers who specify ICs and hybrids for military contracts (the 1987 issue contains data on nearly 150 available product families). A newsletter, *Analog Briefings*, provides current information about the status of reliability at ADI.

### PRICES

Accurate, up-to-date prices are an important consideration in making a choice among the many available product families. Since prices are subject to change, current prices lists and/or quotations are available upon request from our sales offices.

# **Table of Contents**

### Page

ľ

| DSP Processors – Section 2                                                                                                                             |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Introduction                                                                                                                                           |   |

| ADDS-21XX DSP Software Development Tools                                                                                                               |   |

| ADDS-21XX DSP Hardware Development Tools                                                                                                               |   |

| ADSP-2101 In-Circuit Emulator                                                                                                                          |   |

| ADSP-2100/ADSP-2100A 12.5 MIPS DSP Microprocessor                                                                                                      |   |

| ADSP-2101/ADSP-2102 12.5 MIPS DSP Microcomputer                                                                                                        |   |

| AD31-2101/AD31-2102 12.5 Mil 3 D31 Miclocomputer                                                                                                       | 2 |

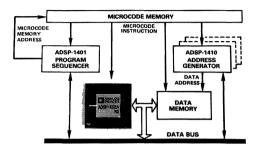

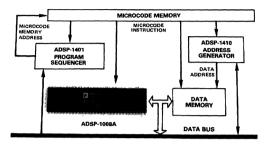

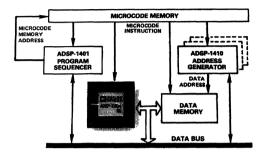

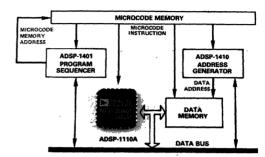

| Microcoded Support Components – Section 3                                                                                                              |   |

| Introduction                                                                                                                                           |   |

| Selection Guide                                                                                                                                        |   |

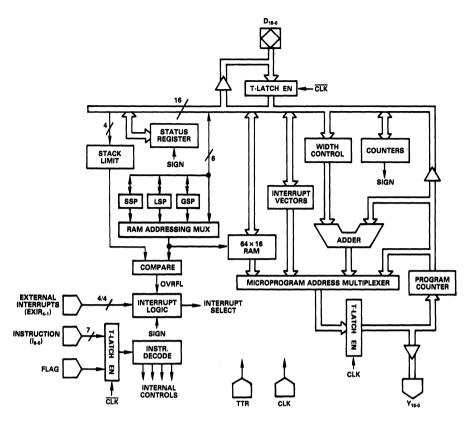

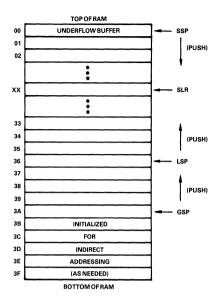

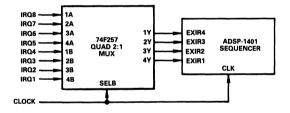

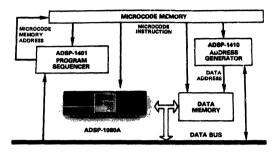

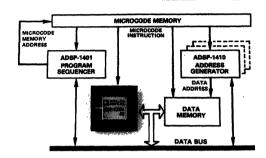

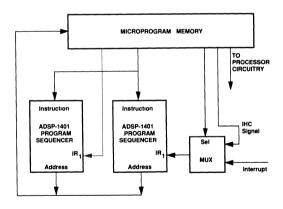

| ADSP-1401 – Word-Slice Program Sequencer                                                                                                               |   |

| ADSP-1402 – Word-Slice Program Sequencer                                                                                                               |   |

| ADSP-1410 – Word-Slice Address Generator                                                                                                               |   |

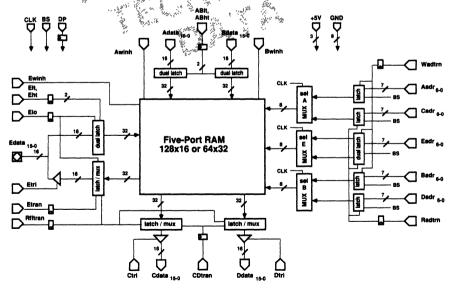

| ADSP-3128A – Multiport Register File $3 - 4$                                                                                                           |   |

|                                                                                                                                                        | 5 |

| Floating-Point Components – Section 4                                                                                                                  |   |

| Introduction                                                                                                                                           |   |

| Selection Guide                                                                                                                                        |   |

| ADSP-3201/ADSP-3202 – 32-Bit IEEE Floating-Point Chipset                                                                                               |   |

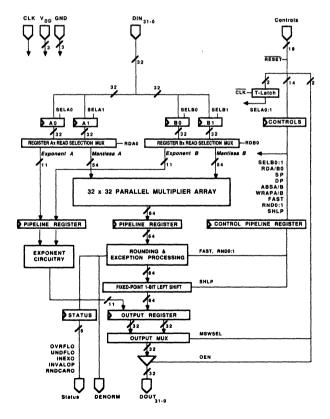

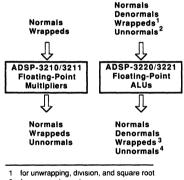

| ADSP-3210/ADSP-3211/ADSP-3220/ADSP-3221 - 64-Bit IEEE Floating-Point Chipsets                                                                          |   |

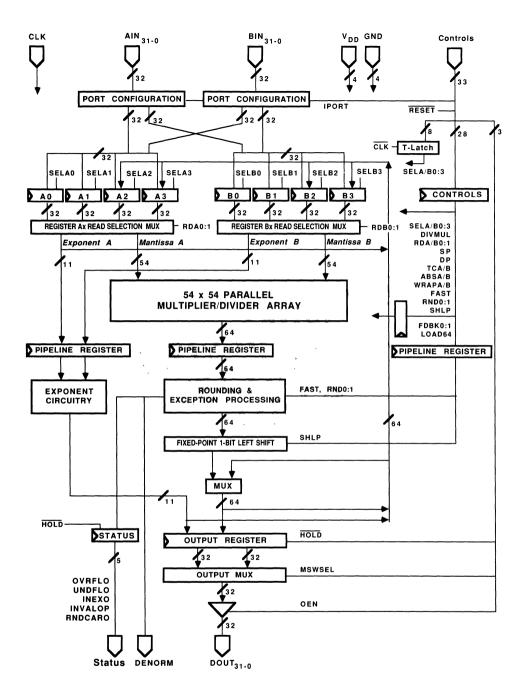

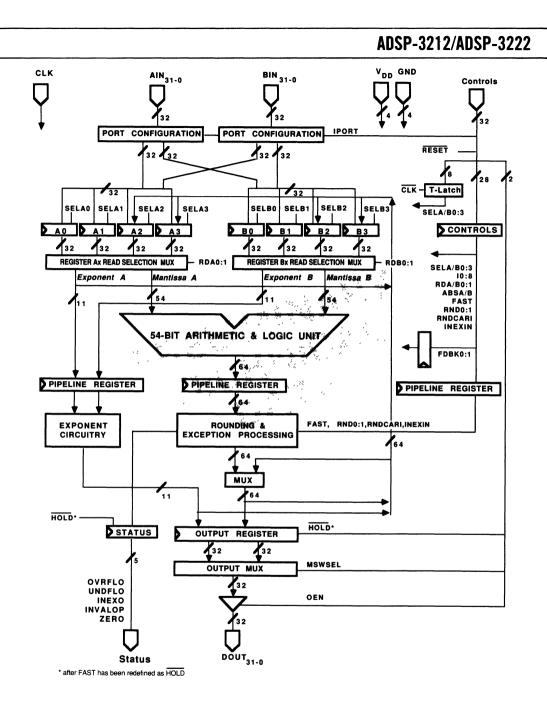

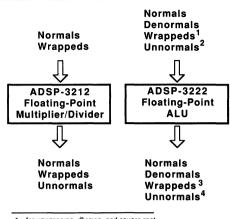

| ADSP-3212/ADSP-3222 – 64-Bit IEEE Floating-Point Chipset                                                                                               |   |

| Fixed-Point Components – Section 5                                                                                                                     |   |

| Introduction                                                                                                                                           |   |

| Selection Guide $\ldots \ldots \ldots$ |   |

| Industry Standard Fixed-Point Components                                                                                                               |   |

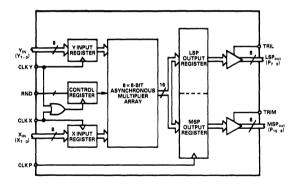

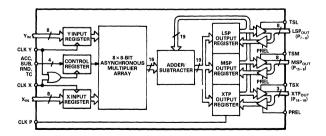

| ADSP-1080A – $8 \times 8$ -Bit Twos Complement CMOS Multiplier                                                                                         |   |

| ADSP-1081A – 8×8-Bit Unsigned-Magnitude CMOS Multiplier                                                                                                |   |

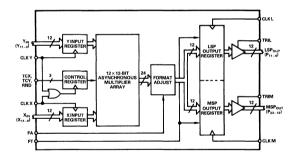

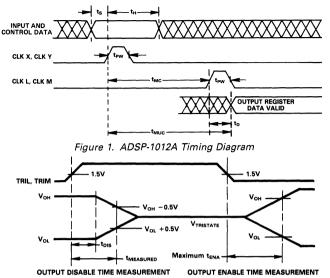

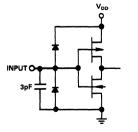

| ADSP-1012A – 12 × 12-Bit CMOS Multiplier                                                                                                               |   |

| ADSP-1016A – 16 × 16-Bit CMOS Multiplier                                                                                                               |   |

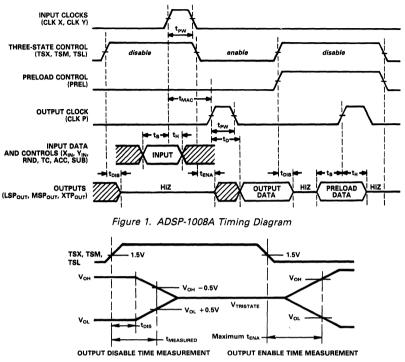

| ADSP-1008A – 8×8-Bit CMOS Multiplier/Accumulator                                                                                                       | 7 |

| ADSP-1009A – 12×12-Bit CMOS Multiplier/Accumulator                                                                                                     | 3 |

| ADSP-1010A – 16×16-Bit CMOS Multiplier/Accumulator                                                                                                     | 9 |

| ADSP-1010B – 16×16-Bit CMOS Multiplier/Accumulator                                                                                                     | 5 |

| Enhanced Fixed-Point Components                                                                                                                        |   |

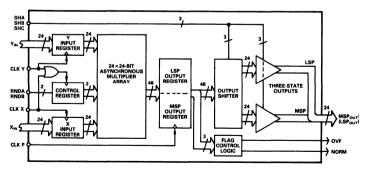

| ADSP-1024A – 24×24-Bit CMOS Multiplier                                                                                                                 | 1 |

| ADSP-1110A – 16 × 16-Bit CMOS Single Port Multiplier/Accumulator                                                                                       | 9 |

| ADSP-1101 – Integer Arithmetic Unit                                                                                                                    | 3 |

| Package Information – Section 6                                                                                                                        |   |

----

### Page

# DSP Processors Contents

|                                                   | Page   |

|---------------------------------------------------|--------|

| Introduction                                      | 2 – 2  |

| ADDS-21XX DSP Software Development Tools          | 2 – 5  |

| ADDS-21XX DSP Hardware Development Tools          | 2 – 11 |

| ADSP-2101 In-Circuit Emulator                     | 2 – 17 |

| ADSP-2100/ADSP-2100A 12.5 MIPS DSP Microprocessor | 2 – 19 |

| ADSP-2101/ADSP-2102 12.5 MIPS DSP Microcomputer   | 2 – 53 |

# Introduction

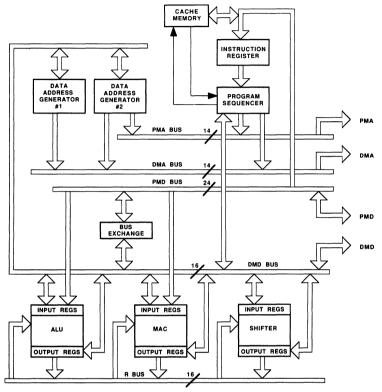

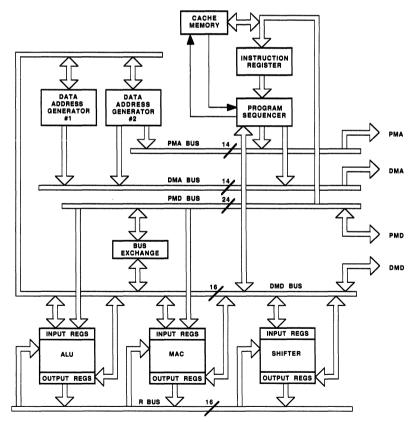

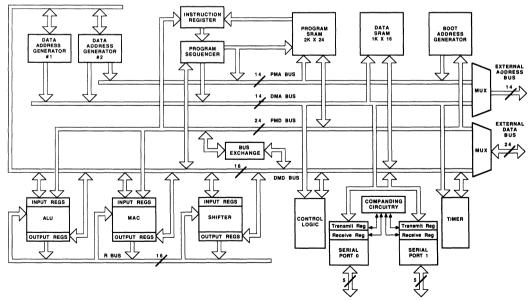

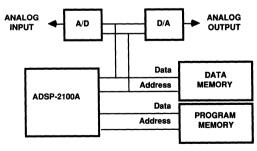

The ADSP-2100 family of digital signal processors provides a core architecture optimized for digital signal processing and other high speed numeric processing applications. The family consists of the ADSP-2100 and ADSP-2100 microprocessors and the ADSP-2101 and ADSP-2102 microcomputers. All devices share the core set of features:

1. Easy-to-Attain High Performance

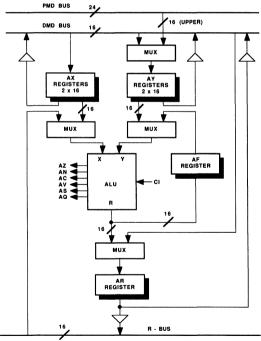

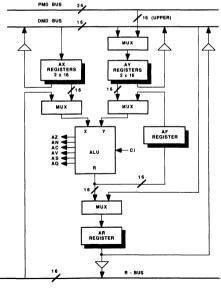

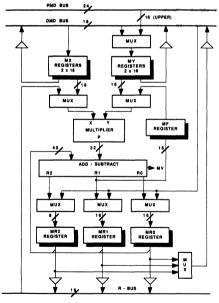

The ADSP-2100 core integrates an arithmetic/logic unit (ALU), multiplier-accumulator (MAC), barrel shifter, data address generators and a program sequencer in a single device. It incorporates modified Harvard architecture (that is, data can also be stored in program memory) for efficient access to program and data memories. The result combines the functions and performance of a bit-slice or building block system with the ease-of-design and development of a generalpurpose microprocessor.

- 2. Easy-to-Understand Instruction Set The ADSP-2100 family instruction set uses an algebraic syntax, similar to high level languages, making it easier to write and understand source code. This results in easier and faster code development and maintenance.

- 3. Easy-to-Use Development Tools & Support The complete set of development tools available for the family (including a C Compiler, Simulator and In-circuit Emulator each described later in this section) minimizes both design time and effort. Your application is up and running faster with this powerful development. In addition, our Applications Engineering Group supports only DSP with application notes, applications handbooks, a customer newsletter, a bulletin board service and excellent telephone support.

- 4. Easy-to-Design System Interface

The advanced design of the ADSP-2100 family allows simple interconnections of memories and I/O devices, minimizes the external logic required to handle interrupts and supports straightforward host interface and multiprocessing designs.

### ADSP-2100/ADSP-2100A Microprocessor

The microprocessor members of the family include the ADSP-2100 and the 1.0 micron ADSP-2100A which are pin and codecompatible. In addition to the core, these devices offer the following:

Modified off-chip Harvard architecture. The processor can access up to 16K words of 16-bit data memory and up to 32K 24-bit words of program memory containing both instructions and data. • A 16-instruction on-chip cache memory with allows the processor to fetch two operands in parallel when executing out of the cache. Since the instruction set supports a high degree of parallelism, the loops of many algorithms can be efficiently coded in 16 instructions or less.

A sample set of benchmarks for the 12.5MHz ADSP-2100A is shown in the table below.

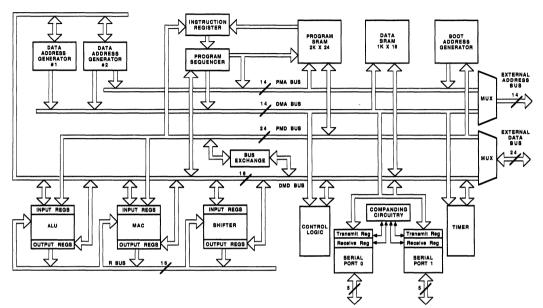

### ADSP-2101/ADSP-2102 Microcomputer

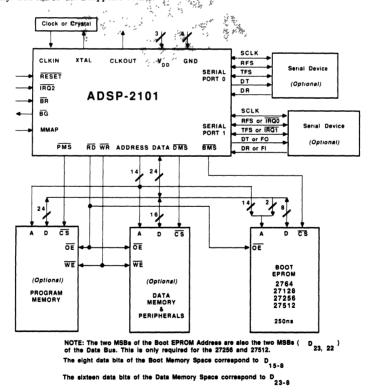

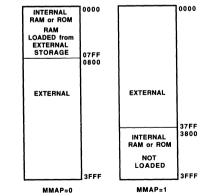

The microcomputer members of the family include the RAMbased ADSP-2101 and the mask programmable ROM-based ADSP-2102. Both are upwardly code compatible with the ADSP-2100 and ADSP-2100A. In addition to the core, these devices offer the following:

- Modified on-board Harvard architecture. The processor has 2K words of (24-bit) program memory RAM and 1K of 16-bit data memory RAM on-chip. Off-chip memories share one address and one data bus which can be used to fetch instructions, data and to boot the processor from external memory.

- A 16-bit programmable timer with an 8-bit prescaling factor that generates its own interrupt.

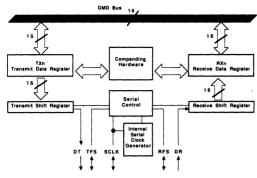

- Two serial ports offering a wide set of possible framing and timing options for interfacing easily to any serial device. Companding is supported in hardware.

The diagram on the following page graphically shows the microprocessor and microcomputer devices.

| ADSP-2100 Family Be                 | nchmarks                                 |

|-------------------------------------|------------------------------------------|

| Algorithm                           | Performance @ 12.5MHz                    |

| FIR Filter                          | 80ns per Tap (1 cycle per Tap)           |

| Complex FIR Filter                  | 320ns per Tap (4 cycles per Tap)         |

| Biquad Filter Section               | 560ns per Section (7 cycles per Section) |

| Lattice Filter Section              | 400ns per Section (5 cycles per Section) |

| 1024-point Complex<br>FFT (Radix-2) | 2.9ms                                    |

| 4096-point Complex<br>FFT (Radix-2) | 19.8ms                                   |

### ADSP-2100/ADSP-2100A

### Core

- ALU, MAC and Barrel Shifter

- Two Data Address Generators, one with bit-reversing capability

- Separate Program Memory and Data Memory address and data buses

- Powerful Sequencer for Zero Overhead looping and singlecycle branches

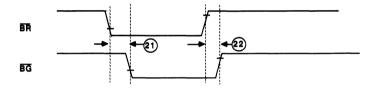

- Bus Grant and Bus Request Signals for host interfacing

- Highly Readable Source Code for ease of development and maintenance

### ADSP-2100/ADSP-2100A Specific Features

- All Program and Data Memory buses extended off-chip

- Single-cycle access to external memory

- Up to 16K of 16-bit word data memory

- Up to 32K of 24-bit word program memory (may also hold data)

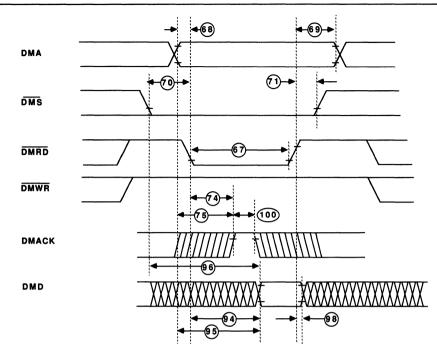

- Data Memory Acknowledge Signal (DMACK) for interfacing to slow, memory-mapped peripherals

- On-chip instruction cache for three bus performance

- Four interrupt request lines

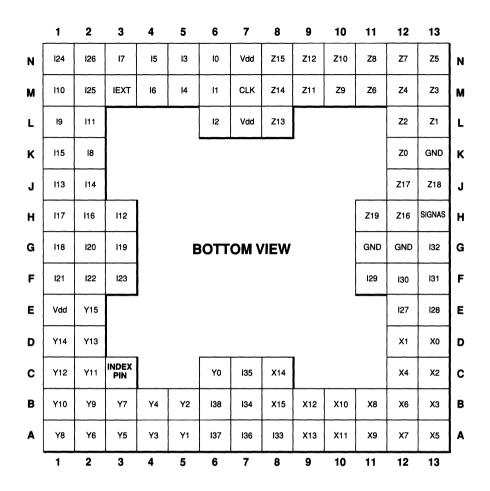

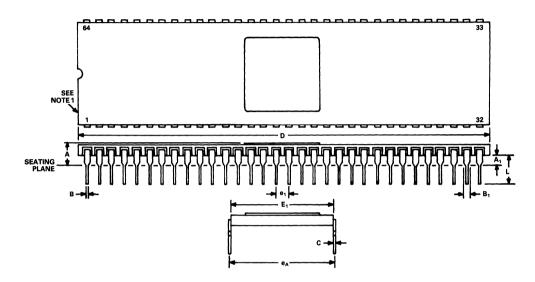

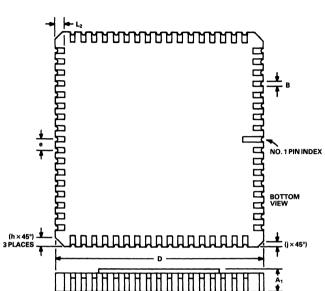

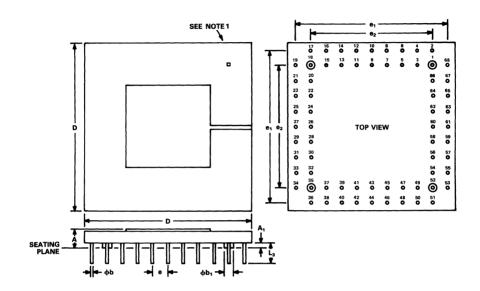

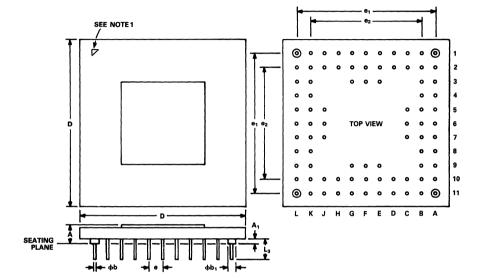

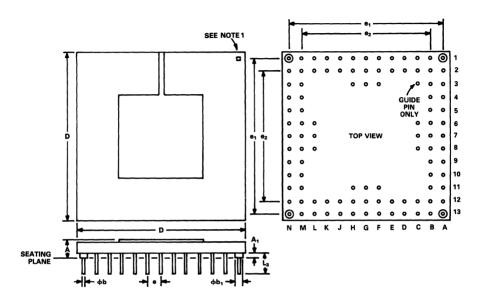

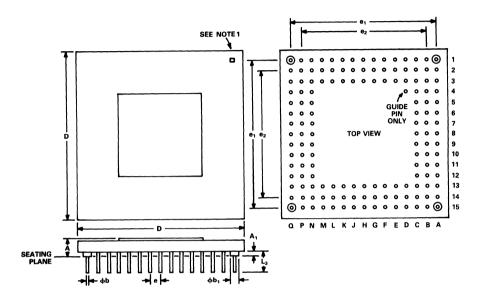

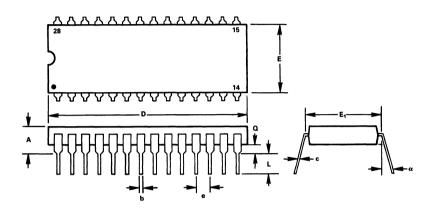

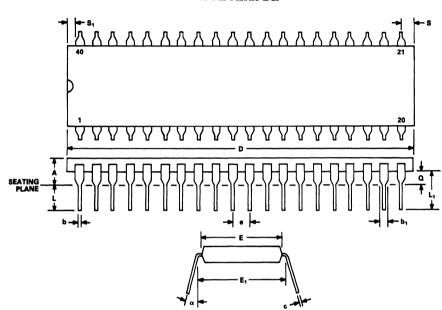

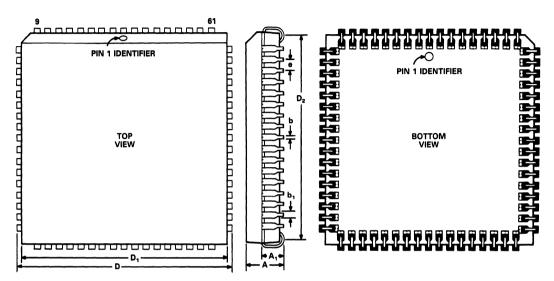

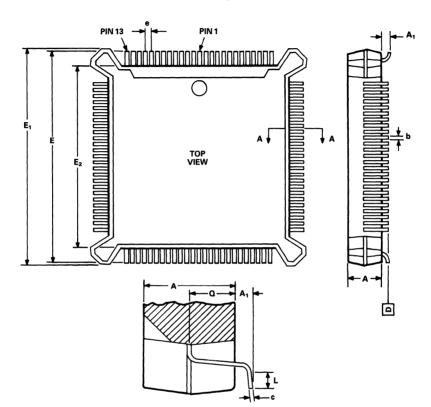

- 100-pin PGA and 100-lead PQFP packages

### ADSP-2101/ADSP-2102

### Core

- ALU, MAC and Barrel Shifter

- Two Data Address Generators, one with bit-reversing capability

- Separate Program Memory and Data Memory address and data buses

- Powerful Sequencer for Zero Overhead looping and singlecycle branches

- Bus Grant and Bus Request Signals for host interfacing

- Highly Readable Source Code for ease of development and maintenance

### ADSP-2101/ADSP-2102 Specific Features

- 2K of 24-bit on-chip program memory RAM

- 1K of 16-bit on-chip data memory RAM

- Up to 16K of 16-bit word data memory using external \_\_\_\_\_\_\_\_\_

- Up to 16K of 24-bit word program memory using external memory

- Up to three memory accesses (one may be off-chip) in a single cycle

- Timer interrupt with programmable period and prescaler

- Two complete serial ports with companding in hardware

- 68-pin PGA and 68-lead PLCC packages

# **DSP Software Development Tools**

# ADDS-21XX

### FEATURES

Release 1.5 Supports the ADSP-2100 and ADSP-2100A DSP Microprocessors

### **C COMPILER**

Programming in C Eases Development of Applications Software

Supports In-Line Assembly Code

Provides FRACT Data Type (1.15 Format) for DSP Algorithms

Complete Calling Interface to Assembly Language Routines

Produces ROMable Code Floating Point Emulation Support Conforms to ANSI Draft Standard (X3J11)

### SYSTEM BUILDER

Architecture Description File Specifies Target Hardware

### ASSEMBLER

Supports High Level Constructs Supports Flexible Macro Processing Encourages Modular Code Development Provides a Full Range of Diagnostics

LINKER Library Support Maps Assembler Output to Target Hardware

PROM SPLITTER Formats ROM Memory Image for Uploading to PROM Programmers

#### SIMULATOR

Interactive User-Friendly Interface Full Symbolic Disassembly Simulates Hardware Configuration Simulates Port I/O Handling Flags Illegal Operations

### **GENERAL DESCRIPTION**

The ADSP-2100 Cross-Software Development tools allow the programmer to develop applications software for implementation on ADSP-2100 and ADSP-2100A DSP microprocessors. The software tools include the C compiler, System Builder, Assembler, Linker, PROM Splitter and Simulator.

### **C COMPILER**

The C Compiler supports the development of application programs in the C programming language. Consisting of a Preprocessor and Compiler which conform to the ANSI draft standard (X3J11), the C Compiler produces ADSP-2100 assembly language source code. Applications written in C are then compiled, assembled and linked to produce code that can be simulated using the Simulator or executed on the Emulator or Evaluation Board.

The Preprocessor supports the complete ANSI draft standard set of options, and reads directives such as *#include*. The *#pragma* directive supports in-line assembly code in a C program. This allows the user to execute efficient assembly language routines within the C environment.

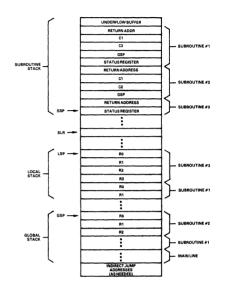

From the code produced by the Preprocessor, the compiler creates a stack-oriented run-time environment using the Data Address Generators to implement the stack. The stack may be located in program or data memory RAM. It is used for parameter passing and local and temporary storage. Because the ADSP-2100 cannot write an immediate value to program memory, locating the stack in data memory is usually more efficient.

The example in Figure 1 illustrates how a simple function implemented in ADSP-2100 source code is interfaced to a C function call.

```

int i, j, k;

main()

ł

k = add(i,j);

}

add(x,y)

#pragma ADSP2100

Function add (x,y)

}

int x.v:

ì

}

ł

Returns: z = x + y;

3

dm(i4,m7) = ay0;

{ save registers }

dm(i4,m7) = ar;

i6 = 1;

{ get first parameter }

modify(i6,m4);

ax0 = dm(i6, m5);

\{m5=1, i6 \text{ points to } 2nd \text{ parameter }\}

av0 = dm(i6.m5);

{ get second parameter }

ar = ax\theta + ay\theta;

{ perform addition }

ax0 = ar:

{ return 16-bit values in ax0 }

i6 = -1:

{ restore registers }

modify(i6, m4);

ay0 = dm(i6, m7);

ar = dm(i6, m7);

#pragma ADSP2100

ļ

```

Figure 1. Assembly Language to C Language Interface

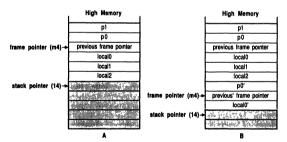

The stack is managed by a frame pointer and stack pointer. The following diagram illustrates the implementation of the stack during a call. The previous frame pointer and local variables are popped unto the stack.

Figure 2. Stack Implementation in ADSP-2100 Memory Space

Though the ADSP-2100 is a 16-bit processor, the C Compiler supports certain 32-bit operations. The following arithmetic data types are supported directly:

| int               | 16-bit twos-complement value          |

|-------------------|---------------------------------------|

| long int          | 32-bit twos-complement value          |

| unsigned int      | 16-bit unsigned value                 |

| unsigned long int | 32-bit unsigned values                |

| fract             | 16-bit fractional value (1.15 format) |

| float             | 32-bit real.                          |

Type *fract* is not a standard C data type but is an extension created to support the 1.15 data format used in digital signal processing applications. The compiler also supports all standard storage classes, types and modifiers.

### 2-6 DSP PROCESSORS

Classes

auto, extern, register, static, typedef

Types

All including void

Modifiers

const, volatile plus pm, dm, ram, rom

Register values, though accepted by the compiler, are not implemented as actual processor registers. The modifiers pm, dm, rom and ram are extensions that are supported. In addition, the fastswitch statement, an extension to the language, has been added to support the DO UNTIL capability of the processors. It is syntactically identical to the standard switch statement but produces faster ADSP-2100 assembly code.

### SYSTEM BUILDER

The System Builder translates a user-defined description of the target hardware system into a form which can be utilized by other Cross-Software Modules. The Cross-Software Modules require knowledge of the target hardware system for the Linker to place relocatable segments, the Simulator to simulate external memory configurations, and for the PROM Splitter to generate separate program and data files. The user specifies the target program memory, data memory and I/O port configurations by writing a System Specification Source File. The System Builder translates this into an Architecture Description File which is read by the other Cross-Software Modules. For example, the Linker resolves the references in the source code and the actual addresses by reading the Architecture File.

The Architecture File is comprised of the following directives that define the ADSP-2100 system:

| .SYSTEM | first statement in .ACH file, specifies the name of the system            |

|---------|---------------------------------------------------------------------------|

| .ENDSYS | last statement in .ACH file, specifies the end of the file                |

| .CONST  | defines constants                                                         |

| .PORT   | declares memory-mapped I/O ports                                          |

| .SEG    | specifies the type of memory in the system (program or data, RAM or ROM). |

The following example of an architecture (.ACH) file shows the use of the directives:

| SYSTEM fir_system,                           | {system name for fir_system} |

|----------------------------------------------|------------------------------|

| SEG/ROM/ABS = 0/PM/CODE program_mem[4096]    | {declare code space}         |

| SEG/RAM/ABS = 4096/PM/DATA coeff_storage[15] | {declare coeff table}        |

| SEG/RAM/ABS = 0/DM/DATA delay_line[15]       | {declare data memory}        |

| PORT/ABS = 16382 ad_sample                   | {declare 1/0 ports}          |

| ENDSYS                                       | {indicates end of file}      |

The .SYSTEM directive defines the name of the ADSP-2100 system. This name is used by the other software modules. The .SEG directive declares memory segments specifying the physical address, segment length, memory area (PM, DM), memory type (RAM, ROM) and memory attributes (CODE, DATA or both). In the above example, *program\_mem* is a 4K-word buffer located in program memory ROM beginning at address 0 consisting of program code. The buffer, *coeff\_storage*, is fifteen words of data located in program memory RAM beginning at address 4096. Finally, *delay\_line* is a 15-word buffer located in data memory RAM starting at address 0. The .PORT directive declares memory-mapped I/O ports by specifying a name for the port and the absolute physical address. In the example, an analog-to-digital converter named *ad\_sample* occupies location 16382 in data memory space.

### ASSEMBLER

The Assembler translates source code modules into relocatable object code modules. The user creates an assembler source code module using the ADSP-2100 Assembly Language and defining variable data buffers and symbolic constants using the Assembler Directives. An assembly module becomes a unit of the complete system source code. Separately assembled object code modules are linked together to form the final running system using the Linker.

Assembler directives support a variety of data and program structures. Invocation switches modify the assembly process.

| .MODULE   | defines the beginning of an assembly module                                                    |

|-----------|------------------------------------------------------------------------------------------------|

| .ENDMOD   | the last statement in a source code file                                                       |

| .VAR      | declare variables and data buffers, the<br>/CIRC qualifier defines circular buffers            |

| .CONST    | declare constants                                                                              |

| .PORT     | declares a memory-mapped I/O port in data memory                                               |

| .INIT     | use to initialize declared variables and data buffers                                          |

| .INCLUDE  | use to read another source file                                                                |

| .MACRO    | defines the beginning of a macro                                                               |

| .ENDMACRO | terminates a macro                                                                             |

| .LOCAL    | use only within a macro, directs the<br>Assembler to create a unique label with<br>local scope |

| .EXTERNAL | assigns external attribute to identifiers declared in other modules                            |

| .GLOBAL   | assigns the global attribute to ports,<br>variables and buffers                                |

| .ENTRY    | assigns entry attribute to label names                                                         |

Macros can be created using the .MACRO directive. For example, the macro shown below is a general purpose memory transfer routine which can transfer data buffers from one memory area (program or data memory) to the other.

{MACRO declaration}

.MACRO memory\_transf (%0, %1, %2, %3, %4); {pass five arguments} .LOCAL transf:

| I4 = %0;                   | {set I4 to source start address}         |

|----------------------------|------------------------------------------|

| I5 = %1;                   | {set I5 to destination start address}    |

| M4 = 1;                    | {set pointer update to single increment} |

| CNTR = %2;                 | {set length of buffer}                   |

| DO transf UNTIL CE;        | {transfer data}                          |

| SI = %3(I4, M4);           | {transfer from type %3 memory}           |

| transf $\%4(15, M4) = SI;$ | {transfer from type %4 memory}           |

| ENDMACRO                   |                                          |

To call the macro within an assembly language program, execute: *memory\_transf (`coeff\_table, `buffer, buff length, PM, DM)*;

### LINKER

The Linker generates the Program Memory/Data Memory Image File, a complete executable program, by linking together object-code modules which were assembled separately. The hardware environment defined by the Architecture File is used by the Linker to place program and data in the defined memory area and location. This output file is used by the Simulator, PROM Splitter, Emulator, and Evaluation Board. Another Linker output, the Debug Symbol Table File, contains a list of all symbols encountered by the Linker and enables the Simulator to utilize user-defined source code level symbols in its interface with user.

To aid the user in interpreting the Linker result, a Map Listing file can be generated.

This file includes:

- A cross-reference listing of all symbols encountered, arranged by module. Information on each symbol such at memory type, absolute address, length and symbol type is given.

- 2. A map of the memory sections and the attributes of each section.

- 3. A map of the allocated segments in program memory, listed sequentially from low order address to high order address.

- 4. A map of the allocated segments in data memory, listed sequentially from low order address to high order address.

- 5. Linker error messages.

- 6. A list of libraries searched and used.

### PROM SPLITTER

The PROM Splitter extracts the address information and the contents of the ROM portion of the PM/DM Image File and formats the extracted images for uploading to PROM burners. Commercially available PROM burners expect input data to be eight bits wide. The PROM Splitter separates the memory image into a byte-wide format. It creates three one-byte wide PROM image files for the 24-bit program memory, and two one-byte wide PROM image files for the 16-bit data memory. Both program and data memory can be optionally output as a single stream of one-byte wide file. The PROM image file is generated in either Motorola S Record, Intel Hex Record or Daisy VLA format. For one-byte wide files, the Motorola S2 format is supported.

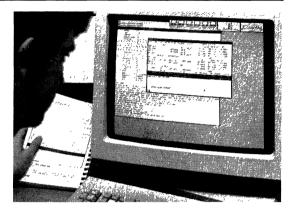

### SIMULATOR

The Simulator simulates the operation of the ADSP-2100 and allows the user to observe the contents of the registers, buses, stacks and program and data memories as a program is being executed. The Simulator is user friendly, interactive and screenoriented. Figure 4 shows the basic Register Display.

| ADSP      | -2100  | Simula  | tor  | V1 5  | Ar   | nalog | Devi       | LCes | In          | ic . |     | SYSTE |       |       |        |      |             |

|-----------|--------|---------|------|-------|------|-------|------------|------|-------------|------|-----|-------|-------|-------|--------|------|-------------|

|           |        | A)      | LU   |       |      |       |            |      |             |      |     | Addre | as Ge | enera | tor #  | 1    |             |

| AX0       | uuuu   |         |      |       |      |       | AC         | 0    | AQ          | 0    | 10  | 0009  | MO    | 0001  | LO     | 000F |             |

| AX1       | uuuu   |         |      |       | R    | սսսս  | AN         | 0    |             |      | 11  | uuuu  | M1    | uuuu  | L1     | 0000 |             |

| AY0       | uuuu   |         |      |       | F    | uuuu  | AV         | 0    |             |      | 12  | uuuu  | M2    | uuuu  | L2     | 0000 |             |

| AY1       | uuuu   |         |      |       |      |       | AZ         | 0    | AS          | 0    | 13  | uuuu  | мз    | uuuu  | L3     | 0000 |             |

|           |        | Multip  | olie | z-Acc | u    | mlato | τ          |      |             |      |     |       | Ad    | dr    |        |      |             |

| NDX 0     | 2000   | -       |      |       |      |       |            |      |             |      |     | Addr  | ess G | ener  | ator i | 2    |             |

| NOC1      | uuuu   | MR2     | 00   | ж     | R1   | 004A  |            | MR   | <b>0</b> 0  | 644  | 14  | 1000  | N4    | 0001  | L4     | 000F |             |

| NYO       | FE8C   |         |      | ж     | 7    | 0000  |            |      |             |      | 15  | uuuu  | N5    | uuuu  | L5     | 0000 |             |

|           | uuuu   |         |      |       |      |       | HV.        | 0    |             |      | 16  | uuuu  | MG    | uuuu  | LG     | 0000 |             |

|           |        |         | Shi  | fter  |      |       |            |      |             |      | 17  | uuuu  | 87    | uuuu  | 1.7    | 0000 |             |

| <b>S1</b> | 2000   | SE u    |      | s     | R1   | uuuu  |            | SR   | <b>0</b> 11 | սսս  |     |       | Ad    | dr    |        |      |             |

|           |        | SBu     |      |       |      |       | <b>S</b> 8 | 0    |             |      | Dat | ta DM | 004A  | PM    | 3C00E  | 5 P1 | <b>x</b> 00 |

| ONTH      | 0000   | Astat   |      | Mst   | a 1. | 0 55  |            |      | 1           | mask |     | c1 00 |       | 0015  |        | 125  |             |

|           |        |         |      |       | . 1  |       |            | IR 3 |             | TINE |     |       | : em  | ilat  |        | ator |             |

| denn      | sim()  | -CMD II |      |       |      |       |            |      |             |      |     |       |       |       |        |      |             |

| 5         | -      |         |      |       |      |       |            |      |             |      |     |       |       |       |        |      |             |

| 5         |        |         |      |       |      |       |            |      |             |      |     |       |       |       |        |      |             |

| \$        |        |         |      |       |      |       |            |      |             |      |     |       |       |       |        |      |             |

| 5         |        |         |      |       |      |       |            |      |             |      |     |       |       |       |        |      |             |

| 5         |        |         |      |       |      |       |            |      |             |      |     |       |       |       |        |      |             |

|           |        |         |      |       |      |       |            |      |             |      |     |       |       |       |        |      |             |

| - re      | gister |         |      |       |      |       |            |      |             |      |     |       |       |       |        |      |             |

Figure 3. Register Display

By reading the Architecture Description File output of the System Builder, the Simulator configures itself to match the target system hardware. This enables the Simulator to flag operations such as attempting to write to ROM or nonexistent memory locations.

The Simulator supports full symbolic disassembly via the Debug Symbol Table File output of the Linker.

The Simulator supports three execution modes: Emulator, Extend and Single-Step. In Emulator mode, the Simulator runs at its fastest speed. The display is updated every 256 cycles. In Extend mode, the display is updated every cycle. In Single-Step mode the Simulator executes a single instruction per run command and updates the screen.

The basic format of the Simulator display includes a status line containing information about the status words, program counter and accumulated cycle time. It also provides a command window for interactive typing of commands and display of error messages and warnings. The Simulator's major informational displays include the following:

| Register         | The register display shows the basic<br>processor data registers (primary or<br>secondary bank), arithmetic status and<br>the state of the buses and data address<br>generators. |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program Memory   | This window displays instructions in<br>fully symbolic form. The user can<br>change opcodes and instructions as<br>needed.                                                       |

| Data Memory      | This window displays the numeric con-<br>tents of data memory.                                                                                                                   |

| Data Memory Plot | This window plots the contents of<br>a selected range of data memory on<br>hardware configurations that support<br>graphics.                                                     |

| Status           | This informational display shows break-<br>points, watchpoints, port status and<br>interrupt status.                                                                             |

| Stack            | The four columns of the Stack window<br>each represent one of the four stacks<br>of the processor. The user can modify<br>the values through push and pop<br>operations.         |

| Trace Buffer     | This displays the history of up to 4K states of the four external buses of the processor.                                                                                        |

| Cache Memory     | This displays (symbolically) the con-<br>tents of cache memory and whether or<br>not an instruction in the cache is<br>deemed valid.                                             |

| Cross Reference  | Displays the location of all symbol names.                                                                                                                                       |

| Modules          | Lists all available modules by name.                                                                                                                                             |

| Help             | Displays a list of Simulator commands<br>and provides further information on<br>them as requested.                                                                               |

In addition, the Simulator allows the user to modify the contents of most registers, memories and status words. Breakpoints can be set in Program Memory and watchpoints in Data Memory. Command files can be created to execute the same set of commands. This is useful for repetitive commands to bring the simulation to a specific starting condition.

User-defined addresses or values can be displayed symbolically. The state of the Simulator can be saved and restored for future simulation sessions. Contents of program and data memory can be dumped to files for use with the hardware development tools. The Simulator supports decimal and hexadecimal numeric formats. I/O to and from ports reads and writes data files which can later be analyzed.

### Simulator Commands

Simulator commands allow the user to change the state of the processor. A quick summary of Simulator commands is shown below. Only the letters shown in caps must be entered to invoke the command.

### Display Control Commands

| Display Control Co  | mmands                                      |

|---------------------|---------------------------------------------|

| ALternate           | displays secondary data registers           |

| BACkup              | forces PM/DM/Trace displays to scroll back  |

| BEep                | enables beeps on user's terminal            |

| CAche               | invokes cache display mode                  |

| DECimal             | forces all numbers to be displayed in deci- |

|                     | mal format                                  |

| DM                  | invokes data memory display mode            |

| FOrward             | forces PM/DM/Trace displays to scroll       |

|                     | forward                                     |

| HELp                | displays command list for access to help    |

| -                   | information                                 |

| HEXadecimal         | forces all numbers to be displayed in hexa- |

|                     | decimal (the default)                       |

| Modules             | displays all source modules                 |

| NOBeep              | suppresses beeps at the user's terminal     |

| NOSymbolic          | forces the simulator to be non-symbolic     |

| PLotdm              | plots the contents of a selected section of |

|                     | DM                                          |

| PM                  | invokes program memory display mode         |

| PRimary             | displays primary data registers             |

| REGister            | invokes register display mode               |

| STACk               | invokes stack display mode                  |

| STATus              | displays Interrupt, Break and Port status   |

| SYmbolic            | forces the simulator to be symbolic         |

|                     | (default)                                   |

| TOggle              | toggles display of primary and secondary    |

|                     | register banks                              |

| TRace               | invokes trace display mode                  |

| Wipe                | rewrites current display                    |

| Xreference          | displays cross-reference list               |

|                     |                                             |

| Operation Control C | Commands                                    |

| EMulator            | invokes emulator mode                       |

| EXTend              | invokes extend mode                         |

| SInglestep          | invokes single-step mode                    |

|                     |                                             |

| Break Control Com   |                                             |

| CLEARBreak          | clears a PM break address                   |

| CLEARStoptime       | clears any stop times currently defined     |

| CLEARWatch          | clears a DM access watch address            |

| COunt               | sets iteration count and delay on break     |

|                     | points                                      |

| SETBreak            | sets a PM break address                     |

| SETStoptime         | sets a time in ns for the processor to halt |

| SETWatch            | sets a DM access watch address              |

|                     |                                             |

#### Context Control Commands

| SETModule | sets the module the Simulator uses for sym |

|-----------|--------------------------------------------|

|           | bolic context                              |

### ADDS-21XX

File Control Commands

| COMmfile                | executes simulator commands found in a batch file         |

|-------------------------|-----------------------------------------------------------|

| DUMPDm                  | forces a DM image dump to a file                          |

| DUMPPm                  | forces a PM image dump to a file                          |

| Load                    | reads .EXE and .SYM files and sets default module context |

| READImage<br>READSymbol | reads a memory image file<br>reads a symbol table file    |

### Modify/Inspect Control Commands

| CLEARTime   | clears the time display               |

|-------------|---------------------------------------|

| CYCLetime   | sets the cycle period in ns           |

| FINDDm      | finds the occurrence of a value in DM |

| FINDPm      | finds the occurrence of a value in PM |

| RESEtstack  | clears stacks and reset pointers      |

| SETDm       | sets a segment of DM                  |

| SETPC       | sets the PC                           |

| SETPM       | sets a segment of PM                  |

| SETRegister | sets a register value                 |

### Assembly Commands

| adds a user-defined symbol name           |

|-------------------------------------------|

| deletes one line of assembly code from PM |

| executes an assembly instruction          |

| patches one line of assembly code into PM |

| deletes a user-defined symbol name        |

|                                           |

### Configuration Control Commands

| BATch      | turns off screen update in Emulator mode             |

|------------|------------------------------------------------------|

| CHipreset  | simulates the hardware chip RESET                    |

| CLOse      | closes a DM memory mapped I/O port                   |

| HArdware   | simulates hardware powerup and sets ROM to undefined |

| Interrupts | activates the interrupt source                       |

| Open       | opens a DM memory mapped I/O port                    |

| POwerup    | simulates the hardware powerup condition             |

### Execution Control Commands

| RUn       | starts processor running in Extend and Em-   |

|-----------|----------------------------------------------|

|           | ulator modes                                 |

| <cr></cr> | starts processor running in Single-step mode |

### Exit Command EXIt

exits from the Simulator and returns to the host

### ADDITIONAL INFORMATION

The ADSP-2100 Software Development System is available for the PC-DOS\*, MS-DOS, VAX/VMS\* and UNIX\* BSD 4.2 on the Sun-3. The ADSP-2100 Cross-Software Manual provides complete information on these tools.

Analog Devices offers a hands-on multiday workshop on programming the ADSP-2100 family of processors. The workshop is taught by our DSP Applications Engineering group and is presented several times a year at the factory in Norwood, Massachusetts. The fee includes all manuals and workbooks and lab time. The workshop can also be conducted at your site; consult us for site pricing.

### **ORDERING INFORMATION**

| Part Number | Description                                                     |

|-------------|-----------------------------------------------------------------|

| ADDS-2110   | Cross-Software for VAX/VMS                                      |

| ADDS-2121†  | System Builder, Assembler, Linker, PROM<br>Splitter for IBM-PC* |

| ADDS-2122†  | Simulator for IBM-PC                                            |

| ADDS-2123-C | Cross-Software for Sun-3 (UNIX BSD 4.2)                         |

| ADDS-2130   | C Compiler and Cross-Software for<br>VAX/VMS*                   |

| ADDS-2131   | C Compiler and Cross-Software for IBM-PC                        |

| ADDS-2133-C | C Compiler and Cross-Software for Sun-3<br>(UNIX BSD 4.2)       |

| ADDS-2190   | ADSP-2100 Family Workshop                                       |

\*PC-DOS and IBM PC are trademarks of International Business Machines Corp. VAX/VMS is a trademark of Digital Equipment Corp. UNIX is a trademark of AT&T.

\*Note that ADDS-2121 and ADDS-2122 must both be ordered to make up a complete IBM-PC Cross-Software system without the C Compiler.

# **DSP Hardware Development Tools**

# ADDS-21XX

2

### FEATURES

ADSP-2100A EVALUATION BOARD Can Be Used to Benchmark Real-Time Performance Interfaces to an IBM-PC or VAX Host via RS-232 Connectors

**Operates at 8MHz**

Same Interactive, Symbolic User Interface as the Emulator and Simulator

Three Execution Modes: Single-Step, Extend, Emulator Displays Contents of ADSP-2100A Registers, Program

Memory, Data Memory and Stack Multiple Program Memory Breakpoints Supported

4K Program and 2K Data Memory Installed with Sockets for Expanding to Full 32K Program and 16K Data Memory

Fully Documented Prototyping Expansion Connector to Customize Evaluation Board to Your Application

Bidirectional Codec Channel to Process Real-World Signals

12-Bit Linear DAC Provides an Oscilloscope Interface Input Preamp with Microphone Jack and Output

Amplifier with Speaker Jack Directly Supports Audio and Speech Applications

ADSP-2100A IN-CIRCUIT EMULATOR

**Performs In-Circuit Emulation**

Interfaces to an IBM-PC or VAX Host via Two RS-232 Connectors

**Operates at 8MHz**

Same Interactive, Symbolic User Interface as the ADSP-2100 Simulator and Evaluation Board

Three Execution Modes: Single-Step, Extend, Emulator Displays Contents of ADSP-2100A Registers, Program

Memory, Data Memory and Stack

Supports Multiple Program Memory Breakpoints

User-Selectable Program Memory Source: Emulator or Target System

User-Selectable System Clock Source: Emulator, Target System or External

OPTIONAL TRACE BOARD FOR IN-CIRCUIT EMULATOR Buffers Up To 8K of Bus Activity for Display and Analysis

Break Triggering on an Extensive Set of Possible Bus Conditions

Buffer Can Be Uploaded to Host for Further Analysis Installs Inside Emulator Case

### GENERAL DESCRIPTION

The ADSP-2100A Hardware Development Tools support the prototyping, development and debugging of applications in hardware.

The Evaluation Board allows the user to benchmark real-time performance by executing Analog Devices-supplied or user-developed DSP routines.

The In-Circuit Emulator allows the user to debug code in the actual target system.

The Trace Board enhances the In-Circuit Emulator by capturing activity on the four external buses of the processor.

The Hardware Development Tools have the same interactive, symbolic user interface as the Simulator. Single-step, extend and emulator execution modes run the processor as required for your debugging activity. Four major display modes enable users to examine contents of ADSP-2100A registers, program memory, data memory and stack. Multiple program memory breakpoints are supported.

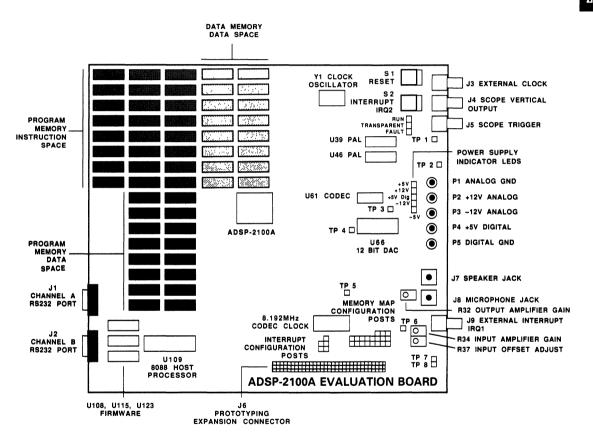

### ADSP-2100A EVALUATION BOARD

The Evaluation Board is an easy-to-use development tool for evaluating the ADSP-2100A DSP Microprocessor in real-time applications. It has three roles in the design process. As a demonstration system, you can observe the ADSP-2100A's real-time performance in executing standard DSP benchmarks. As an evaluation system, it can be used prior to designing hardware for the real-time execution of your application routines. As a simulation accelerator, application code can be executed in real time for increased productivity of software developers. The Evaluation Board is a stand alone system consisting of an ADSP-2100A DSP Microprocessor, 4K words of (24-bit) program memory, and 2K words of (16-bit) data memory. Additional program and data memory sockets are provided and can be populated as desired up to the full 32K program and 16K data memory address space.

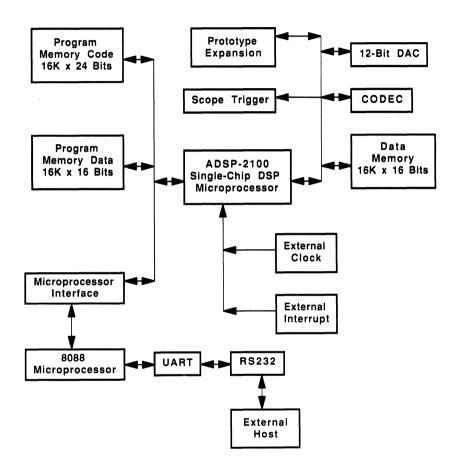

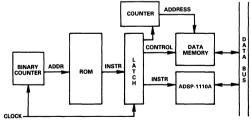

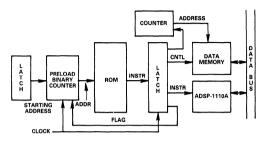

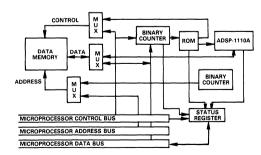

Figure 1. Evaluation Board Block Diagram

### ADDS-21XX

The Evaluation Board's ADSP-2100A runs under the control of an on-board host processor enabling the user to access a variety of powerful debugging tools. When interfaced to an external host computer system running the Cross-Software, the Evaluation Board serves as a real-time development tool.

The emulator mode runs the processor at full speed. Extend mode updates the screen every cycle during program execution. Single-step mode executes a single instruction per carriage return. In addition, multiple program memory breakpoints are supported. The Evaluation Board has four major display modes: register, program memory, data memory and stack. Register mode displays the contents of the ADSP-2100A's primary and alternate registers. Program memory mode displays the contents of program memory. Data memory mode displays the contents of data memory. Stack display shows the contents of the ADSP-2100A's program counter stack and count stack.

The Evaluation Board connects to a terminal and host computer via two RS-232C serial connectors.

Figure 2. Evaluation Board

Built-in analog interfaces provide access to real signals for easy implementation of audio, speech and telecommunications applications. A bidirectional codec channel and an undedicated 12-bit linear D/A converter process real-world signals. The prototyping expansion bus allows you to construct custom hardware to reflect or test the eventual hardware environment. In addition, three BNC connectors interface to external instrumentation. An integral microphone jack and input pre-amplifier, along with a speaker jack and output amplifier, support speech and telecommunication applications.

With a microphone, speaker and oscilloscope you can easily implement audio and speech applications. The microphone and speaker are connected to the bidirectional codec channel via jacks on the input preamp and output amplifier. The codec is a National Semiconductor TP3051. It is a memory-mapped peripheral of the ADSP-2100A that can be written to or read from using the Data Memory Read and Data Memory Write commands. The codec represents the input/output sample in an 8-bit binary form. By using the standard µ-law nonlinear transformation, the codec's effective dynamic range can be extended to 13 bits. The codec samples data at a frequency of 8.192kHz using a dedicated clock generator. Communication between the codec and the ADSP-2100A is synchronized with the DMACK signal. The codec rejects signals that do not fall in the range of 200Hz to 3400Hz and should be used only in speech or audio applications in which telephone-quality signals are adequate. An input pre-amplifier (Analog Devices AD741 operational amplifier) and output audio amplifier (National Semiconductor LM338 Audio Power Amplifier) are connected to the input and output of the codec.

To display processed data, the oscilloscope is connected to the 12-bit linear DAC via a BNC connector. The DAC is an Analog Devices AD667 12-bit D/A converter. It is a memory-mapped peripheral of the ADSP-2100A that can be written using the Data Memory Write commands. The DAC is intended for use as an analog output for the display of processed data on an oscilloscope. It is not intended as a means of reconstructing sampled data processed by the ADSP-2100A; it lacks the deglitching circuitry and anti-imaging filtering required of such a system. The user can construct a linear analog interface consisting of an A/D converter, D/A converter, antialiasing filter and anti-imaging filter using the prototyping expansion connector.

The prototyping expansion connector provides the data, address and interface signals for customizing the Evaluation Board. For example, analog circuitry composed of linear A/D and D/A converters and antialiasing filters may be connected to the Evaluation Board for implementing filtering applications. The 96-contact prototyping expansion connector brings out the following signals:

### **Input Signals**

| 1 0            |                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------|

| EIRQ3          | External Interrupt Request 3 (Highest Priority)                                                          |

| EIRQ2          | External Interrupt Request 2                                                                             |

| EIRQ1          | External Interrupt Request 1                                                                             |

| EIRQ0          | External Interrupt Request 0                                                                             |

| EBR            | External Bus Request . Allows your target board to request control of the data memory interface.         |

| EDMACK         | Data Memory Acknowledge. Used for asynchronous transfers across the data memory interface.               |

| THALT          | Processor Halt by Target System. Assertion of THALT halts the ADSP-2100A.                                |

| RESETOUT       | System Reset Output. The ADSP-2100A's RE-<br>SET line is available at this contact as an output<br>only. |

| Output Signals | 5                                                                                                        |

| +12V           | +12V Analog                                                                                              |

| AGND           | Analog Ground                                                                                            |

|         | 6                                                                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND    | Analog Ground                                                                                                                                        |

| -12V    | -12V Analog                                                                                                                                          |

| GND     | Digital Ground                                                                                                                                       |

| BG      | Bus Grant. Acknowledges an external bus request ( $\overline{BR}).$                                                                                  |

| DMA13-0 | Data Memory Address bits                                                                                                                             |

| DMRD    | Data Memory Read. Indicates a read operation on the data memory interface.                                                                           |

| DMWR    | Data Memory Write. Indicates a write operation on the data memory interface.                                                                         |

| DMS     | Data Memory Select. Signals a data memory access on the data memory interface.                                                                       |

| TRAP    | Indicates the execution of a TRAP instruction.<br>The ADSP-2100A halts execution and the<br>TRAP signal remains asserted until THALT is<br>asserted. |

| ECE8-1  | External Chip Enables 8 through 1. These outputs are memory-mapped locations.                                                                        |

#### **Bidirectional Signals**

DMD15-0 Data Memory Data Bus

The Evaluation Board must be interfaced to an IBM-PC (with VT100 emulation) or VAX/VMS system via the RS-232 connectors. This host computer must also run the ADSP-2100 Cross-Software. The board requires  $\pm 12V$  and  $\pm 5V$  power supplies.

### ADSP-2100A IN-CIRCUIT EMULATOR

The In-Circuit Emulator allows you to debug code (developed with the Software Development tools) in the actual target system. The Emulator uses an ADSP-2100A to emulate the processor. It plugs into the target system's ADSP-2100A socket and operates at the ADSP-2100A's cycle rate. The Emulator provides a software interface similar to the Cross-Software Simulator and to the Evaluation Board.

Once your program has been debugged in the software environment you can further prove and debug in the hardware area using the Emulator. It provides a variety of ways to download your program into the actual hardware, executing out of emulator program memory or target system program memory, for example, or using any of three sources for the system clock.

The Emulator supports three execution modes. In emulator mode the Emulator runs at the full processor speed and halts only when a break condition is encountered. Break conditions include breakpoints, traps, halt on keyboard interrupt and target system voltage below 4.5V. While the Emulator is running in emulator mode, only the program counter and elapsed time information is updated. When the Emulator halts, the full screen is updated.

Extend mode runs the processor in a continuous single-step manner, updating the display after each processor cycle. Instructions are disassembled on the screen as they are executed. In emulator and extend modes, emulation can be halted by setting a breakpoint at a specified location in program memory.

In single-step mode, the Emulator executes one instruction and halts. All display contents are updated and instructions are disassembled as they are executed. The next instruction is executed if you type a carriage return or enter the RUN command.

The Emulator has four major display modes (five with the Trace Board installed). Register display shows the contents of the ADSP-2100A's primary and secondary registers. The program memory and data memory displays show the contents of program and data memories. Stack display shows the contents of the ADSP-2100A's program counter stack and count stack.

Using the same interactive, symbolic user interface as the Simulator, the Emulator allows the user to modify the contents of registers, program memory, data memory and the program counter. Breakpoints can be set in the emulator-based program memory. User-defined addresses and values can be displayed symbolically. Numbers can be specified and displayed in either decimal or hexadecimal format.

The Emulator has other features. The baud rate and parity settings for communications between the Emulator and the host computer can be specified by the user's terminal. The Emulator Pod can be activated and deactivated under software control. The program memory source can be either the Emulator's internal program memory RAM or the target system's program memory. Also, files can be downloaded from the host system. The system clock can be selected from either the Emulator's internal clock, the target system's clock or an external clock generator.

### **Propagation Delays**

Although the Emulator matches the ADSP-2100A closely in performance for a few signals, its timing is degraded somewhat from that of the processor. Propagation delays and, in some cases, software overhead account for the delays. The signals with degraded timing are:

- CLKIN

- IRO

- BR

- RESET

- HALT

- TRAP

- PMWR and PMRD

All other signals operate at essentially the same timing as the processor in a non-emulator system. Complete information and timing diagrams are given in Appendix B of the *ADSP-2100 Emulator Manual*.

### TRACE BOARD FOR ADSP-2100A IN-CIRCUIT EMULATOR

The Emulator supports an optional, factory-installed Trace Board. The Trace Board keeps a running history of past external bus states PMA, DMA and DMD in an 8K buffer. The Trace Buffer Display shows the past external bus states of the ADSP-2100A.

The Trace Board allows you to trigger on bus conditions. Emulation can be halted after detecting a specified combination of bus states. The IGNORE option turns off the trace during certain PMA ranges in order to skip over sections of code. The Trace Board can trigger on the following eleven different bus combinations:

PMA AND DMA PMA AND DMD DMA AND DMD PMA AND DMA AND DMD PMA OR (DMA AND DMD) DMA OR (PMA AND DMD) DMD OR (PMA AND DMA) PMA OR DMA OR DMD (PMA AND DMA) OR (PMA AND DMD) (PMA AND DMA) OR (DMA AND DMD)

In addition, the trace buffer can be uploaded from trace board to host computer.

### ADDITIONAL INFORMATION

Request the ADSP-2100 Emulator Manual or the ADSP-2100 Evaluation Board Manual from your Analog Devices Sales Engineer for further information.

### ORDERING INFORMATION

| Part Number  | Description                                                    |

|--------------|----------------------------------------------------------------|

| ADDS-2150A*  | 8MHz ADSP-2100A In-Circuit Emulator<br>(110V)                  |

| ADDS-2150AE* | 8MHz ADSP-2100A In-Circuit Emulator<br>(220V)                  |

| ADDS-2151A*  | 8MHz ADSP-2100A In-Circuit Emulator<br>with Trace Board (110V) |

| ADDS-2151AE* | 8MHz ADSP-2100A In-Circuit Emulator<br>with Trace Board (220V) |

| ADDS-2160*   | 8MHz ADSP-2100A Evaluation Board                               |

| Upgrade Kits |                                                                |

| ADDS-2161    | Trace Board Upgrade for ADDS-2150                              |

| ADDS-2162    | Trace Board Upgrade for ADDS-2150A                             |

\*A 12.5MHz version of this product is planned. Please contact factory for further information.

# ANALOG DEVICES

# In-Circuit Emulator ADSP-2101

### FEATURES

Supports the ADSP-2101 DSP Microcomputer Performs In-Circuit Emulation

- Operates at the Full Clock Rate of the ADSP-2101 (12.5MHz)

- Same Interactive, Symbolic User Interface as the ADSP-2101 Simulator

Single-Step, Full Speed and Periodic Update Execution Supports Breakpoints and Triggers

- User Selectable Memory Source: Emulator or Target System

- User Selectable Clock Source: Emulator or Target System

- RS-232C Interface to Host System Supporting Up to 19.2 kb/s

8K Trace Buffer

**On-Line Assembly/Disassembly**

Performance Analysis

Histogram Profiling of Executing Code Time-Tags on Trace Buffer Contents

Modular Hardware Based on VME Bus

### **GENERAL DESCRIPTION**

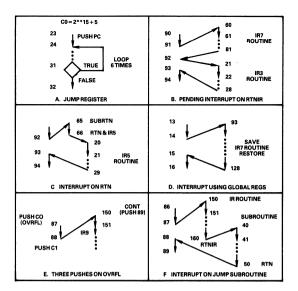

The ADSP-2101 In-Circuit Emulator allows the user to debug code developed with the ADSP-210X Cross Software Modules in an actual target system. The Emulator, which uses an ADSP 2101 to emulate the processor, plugs into the target system's ADSP-2101 socket and operates at the ADSP-2101's cycle-fate. The Emulator supports three different types of memories: program memory, data memory and boot memory. All memories can be downloaded by the user. The boot memory interface is supported. The Emulator can operate from either emulator or target system based memory.

The Emulator can run at the full processor speed updating the display only when execution halts. The Emulator can also run in semi-real time updating the display at a predetermined rate up to every cycle. The user can also single-step through code from the keyboard.

The Emulator displays information about the state of the emulation in a variety of windows, similar to the ADSP-2101 Simulator. These include register, memory, execution profile and trace

windows. The contents of the ADSP-2101's registers are displayed including serial port control registers, interval timer control registers and memory mapped registers. The memory windows can show the contents of all memories on and off chip including boot memory. The trace display shows the contents of the 8K deep trace buffer. The execution profile shows the use of program modules to measure the efficiency and performance of code.

The Emulator allows the user to modify the contents of registers and memory. Breakpoints can be set and user-defined addresses and values can be displayed symbolically. For ease of use, the user can either specify decimal or hexadecimal format.

On-line assembly allows users to modify the code starting at a specified location and load instructions on a line-by-line basis. The disassembled contents of each address can be displayed before a new assembled instruction is stored.

The Emulator supports an 8192-frame deep trace buffer that stores data and address buses as well as control signals. Triggering on bus events, control lines and serial ports is supported. These events can be logically ANDed, ORed or negated to define a trigger event.

Consult the factory for current status.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

# **12.5 MIPS DSP Microprocessor**

## ADSP-2100/ADSP-2100A

### FEATURES

Pin- and Code-Compatible DSP Microprocessors ADSP-2100, 6.144MHz and 8.192MHz ADSP-2100A, 10.24MHz and 12.5MHz Separate Program and Data Buses, Extended Off-Chip Single-Cycle Direct Access to 16K × 16 of Data Memory Single-Cycle Direct Access to 32K × 24 of Program Memory **Dual Purpose Program Memory for Both Instruction** and Data Storage Three Independent Computational Units: ALU, Multiplier/Accumulator and Barrel Shifter **Two Independent Data Address Generators Powerful Program Sequencer** Internal Instruction Cache **Provisions for Multiprecision Computation and** Saturation Logic Single-Cycle Instruction Execution **Multifunction Instructions** Four External Interrupts 80ns Cycle Time (ADSP-2100A) 790mW Maximum Power Dissipation (ADSP-2100A, J and K Grades) 100-Pin Grid Array, 100-Lead PQFP (JEDEC Style) APPLICATIONS **Optimized for DSP Algorithms Including**

Digital Filtering Fast Fourier Transforms Applications Include Image Processing Radar, Sonar Speech Processing Telecommunications

### **GENERAL DESCRIPTION**

The ADSP-2100 and ADSP-2100A are pin- and code-compatible single-chip microprocessors optimized for digital signal processing (DSP) and other high-speed numeric processing applications. The ADSP-2100 and ADSP-2100A are both fabricated in a lowpower double-layer metal CMOS process. Together, they offer a span of performance from 6MHz to 12.5MHz. All descriptions of the ADSP-2100 in the text of this data sheet refer to both the ADSP-2100A and the ADSP-2100 versions since they have identical architectures and instruction sets. Timing and electrical specifications differ as shown in those sections of the data sheet.

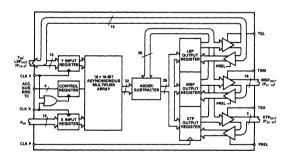

Both processors integrate computational units, data address generators and a program sequencer in a single device. The ADSP-2100 architecture makes efficient use of external memories for program and data storage, freeing silicon area for increased

processor performance. The resulting processor combines the functions and performance of a bit-slice/building block system with the ease of design and development support of a general purpose microprocessor.

The ADSP-2100A (K grade) operates at 12.5MHz. Every instruction executes in a single 80ns cycle. The ADSP-2100A (J and K grades) dissipates less than 790mW while the ADSP-2100 dissipates less than 475mW.

The ADSP-2100's flexible architecture and comprehensive instruction set support a high degree of operational parallelism. Because all instructions execute in a single cycle, MHz = MIPS. In one cycle the ADSP-2100 can:

- generate the next program address

- fetch the next instruction

- · perform one or two data moves

- update one or two data address pointers

- perform a computational operation.

### DEVELOPMENT SYSTEM

The ADSP-2100 and ADSP-2100A are supported by a complete set of tools for software and hardware system development. The Cross-Software System provides a System Builder for defining the architecture of simulated systems under development, an Assembler, a Linker and a interactive Simulator. An ANSI (draft) Standard C Compiler supports program development in this widely used programming language, producing ADSP-2100 Assembly code which may be assembled, linked and simulated with the other development system tools. A PROM Splitter generates PROM burner compatible files. An In-Circuit Emulator is available for hardware debugging.

An Evaluation Board is available for quick assessment of actual processor performance in a prepackaged hardware environment.

### ADDITIONAL INFORMATION

For additional information on the architecture and instruction set of the processor, refer to the ADSP-2100 User's Manual. For more information about programming and the Development System, refer to the ADSP-2100 Cross-Software Manual and the ADSP-2100 Emulator Manual. For examples of applications routines, refer to the ADSP-2100 Applications Handbook, Volume 1 or Volume 2. Manuals are available only from your local Analog Devices sales office. There is also a quarterly newsletter, DSPatch<sup>TM</sup>, supporting Analog Devices' digital signal processing customers.

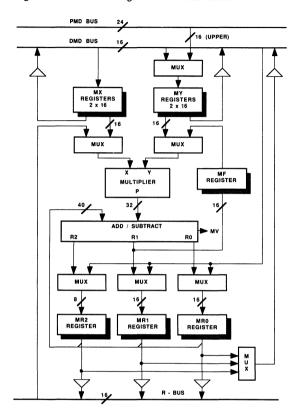

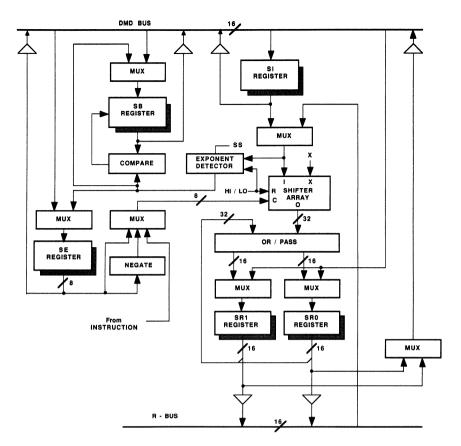

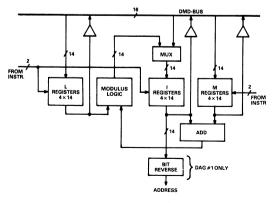

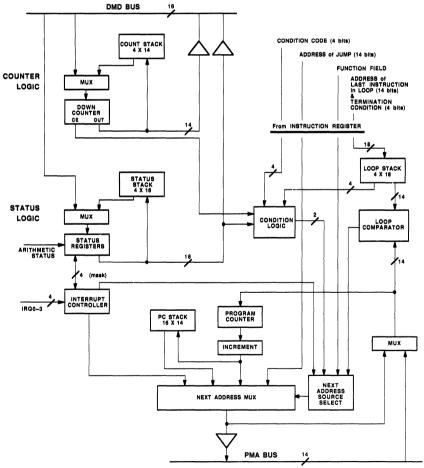

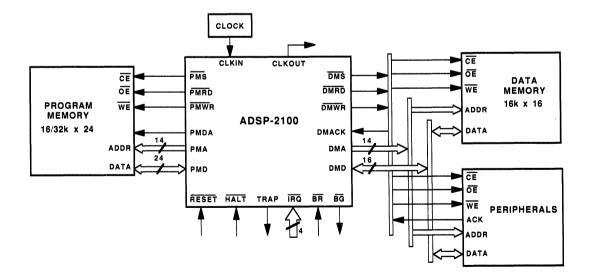

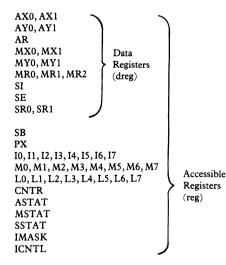

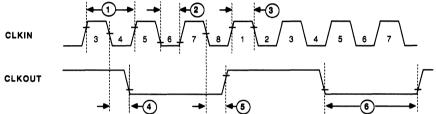

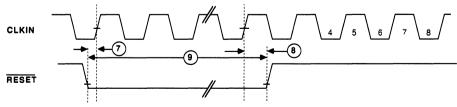

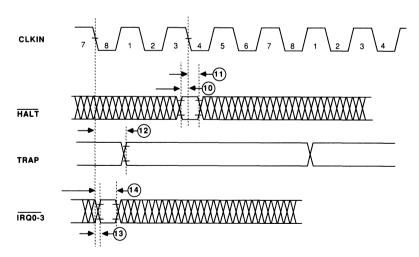

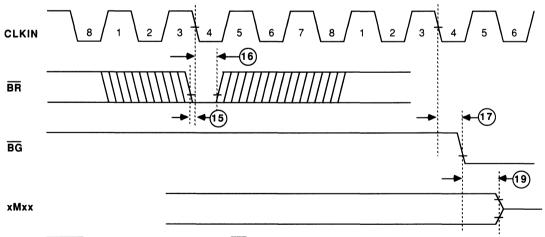

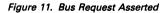

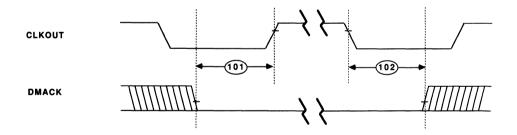

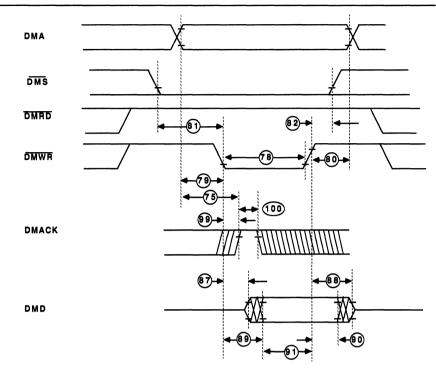

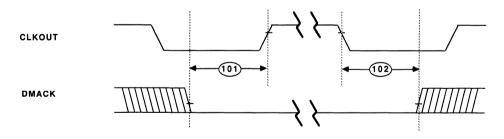

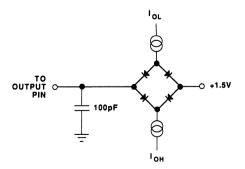

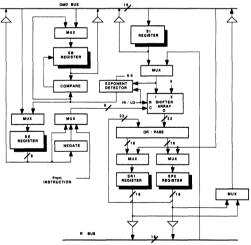

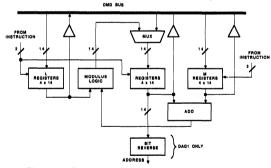

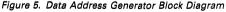

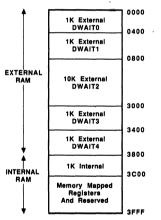

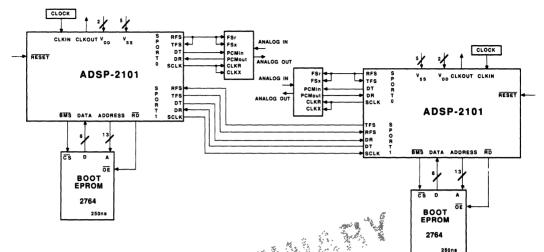

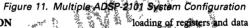

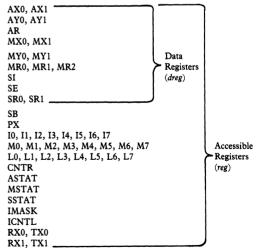

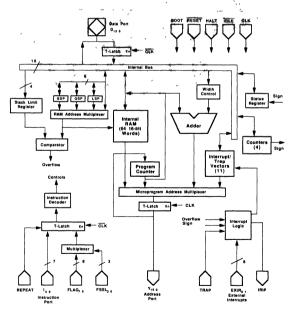

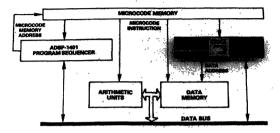

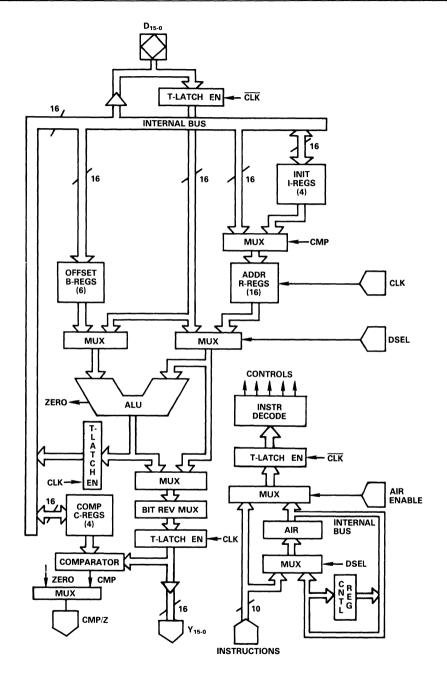

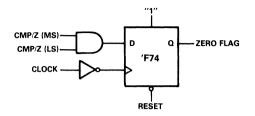

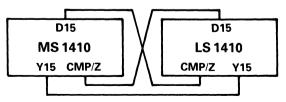

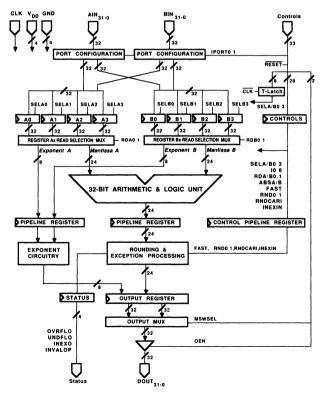

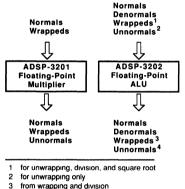

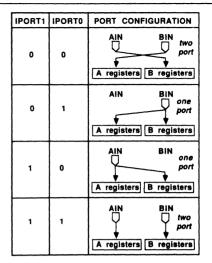

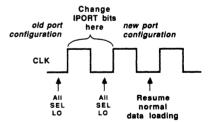

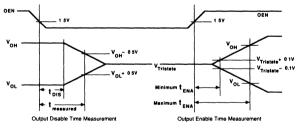

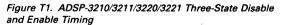

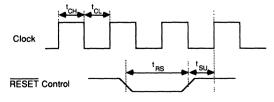

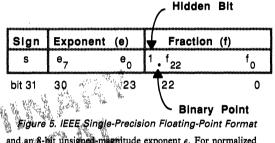

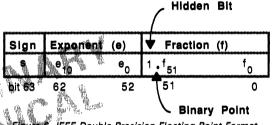

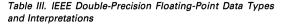

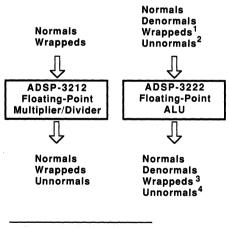

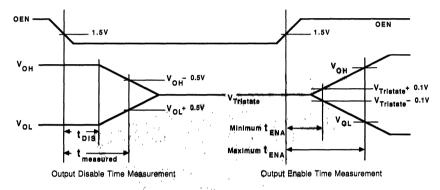

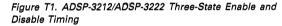

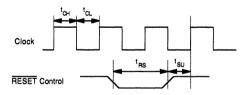

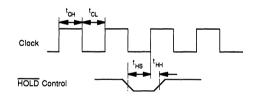

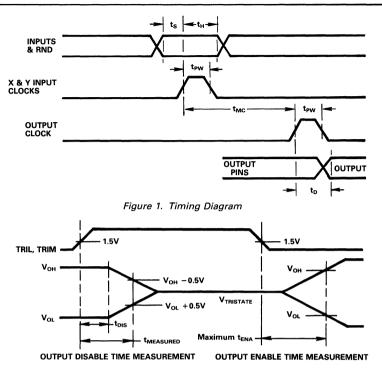

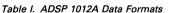

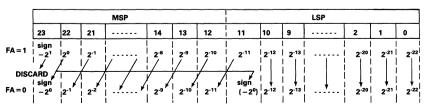

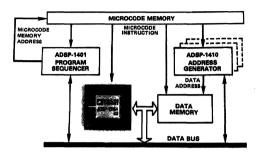

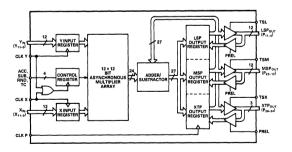

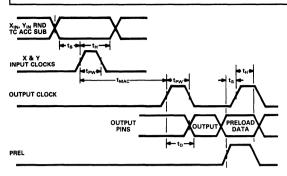

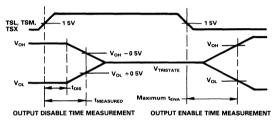

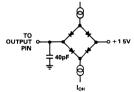

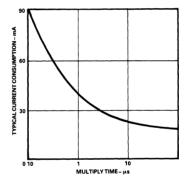

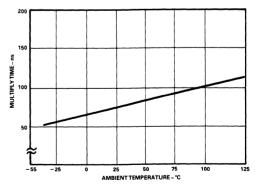

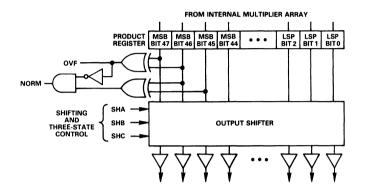

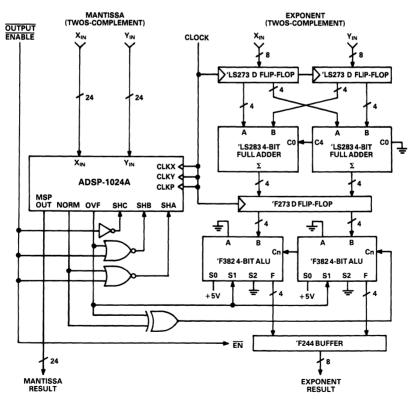

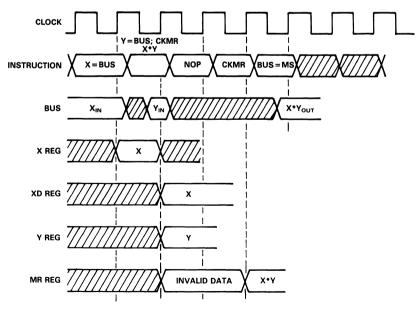

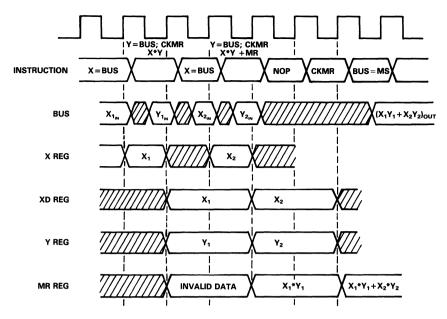

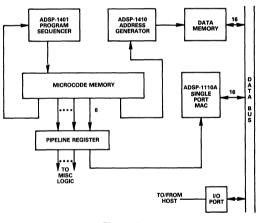

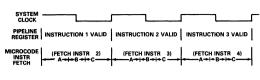

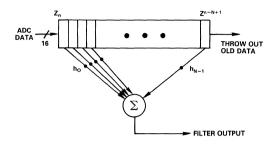

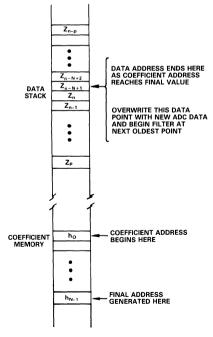

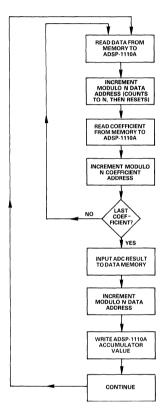

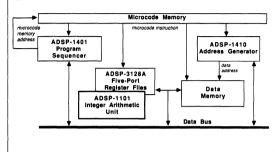

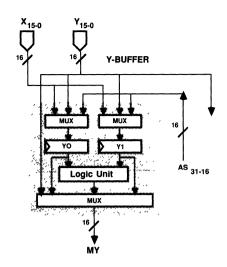

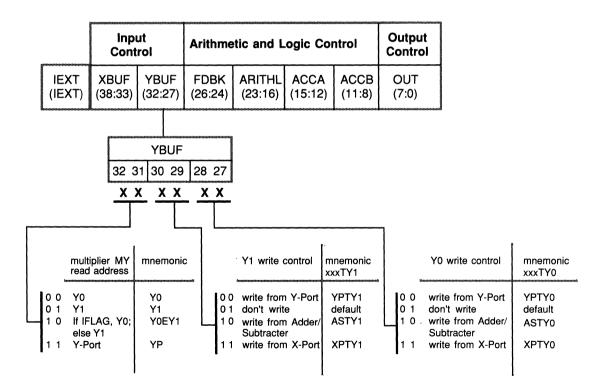

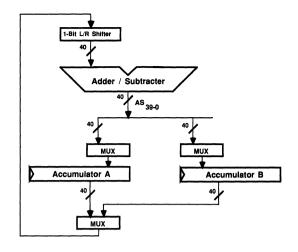

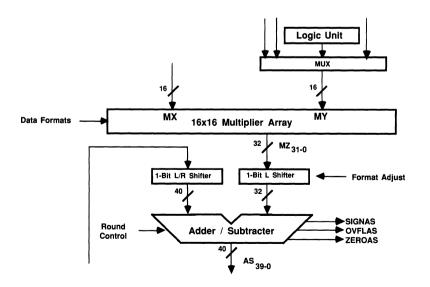

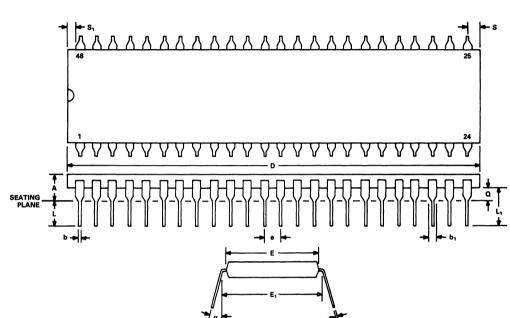

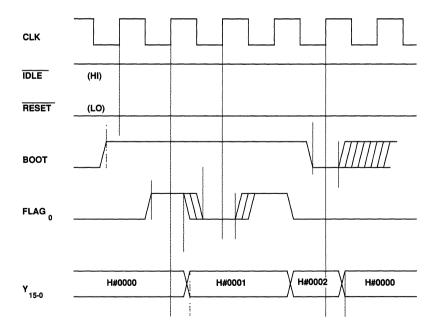

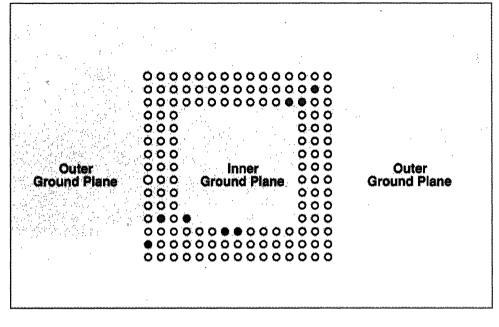

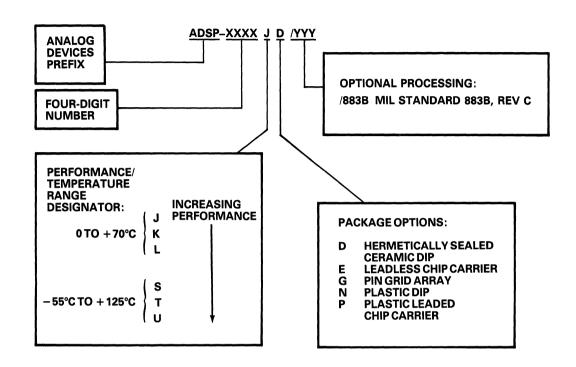

### **ARCHITECTURE OVERVIEW**